Im Folgenden werden die wichtigsten Merkmale eines FPAAs in verallgemeinerter Form dargestellt. Für genauere Informationen bezüglich der spezifischen Architektur eines bestimmten FPAAs suchen Sie bitte die Internetseiten des betreffenden Herstellers auf, die Sie hier finden:: AN10E40, AN220E04, TRAC020, IspPAC30.

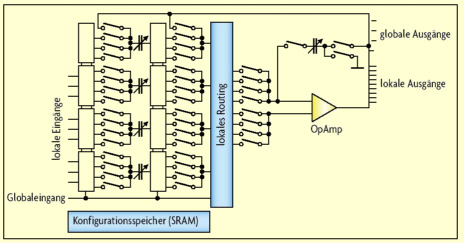

Ein FPAA enthält eine matrixförmige Anordnung von 4 bis 20

konfigurierbaren analogen Grundzellen, den so genannten "configurable analog

blocks" (CABs). Diese sind je nach Hersteller und Produkt unterschiedlich

aufgebaut, weisen aber einige Gemeinsamkeiten auf. So beinhaltet ein CAB

in der Regel

- mindestens einen Operationsverstärker

- konfigurierbare Kapazitäten und Widerstände

- konfigurierbare Verbindungsresourcen (Leitungen, Schalter)

- Speicher für die Konfigurationsdaten (meist SRAM)

- Ein- und Ausgänge

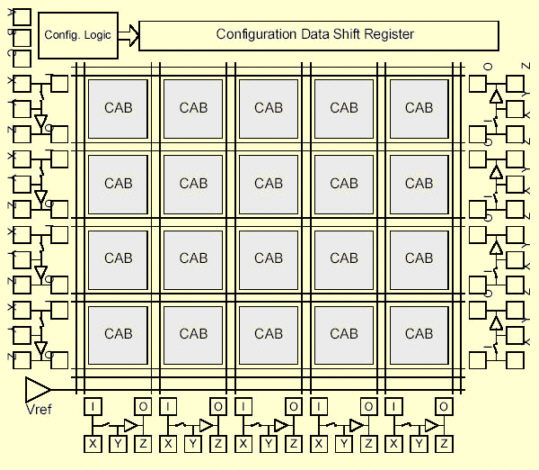

Die CABs sind eingebettet in ein Gitter konfigurierbarer Verbindungsleitungen, die die Verschaltung der CABs miteinander und mit der "Umwelt" erlauben.

Als Schnittstelle zwischen CABs und Umwelt enthält ein FPAA mehrere I/O-Zellen, die unidirektional (nur Eingang oder nur Ausgang) oder bidirektional funktionieren können.

Die konfigurierbaren Widerstände werden in der Regel durch geschaltete Kapazitäten (switched capacitors) realisiert, um Chipfläche zu sparen. Näheres zur SC-Technik finden Sie hier.

Bezüglich der Rekonfigurierbarkeit unterscheidet man FPAAs, die im laufenden Betrieb (dynamisch) umkonfiguriert werden können und solchen, die zum Einlesen neuer Konfigurationsdaten ihren Betrieb aussetzen müssen. Zur ersten Klasse gehört das AN10E40, zur zweiten Klasse das AN220E04.

Zur Veranschaulichung wird nachfolgend der prinzipielle Aufbau eines CABs an Hand des AN10E40 dargestellt. Als Besonderheit beinhaltet er ein Netz von "switched capacitor"-Schaltungen, das hier aber nicht näher betrachtet werden soll:

Quelle: Anadigm

Um die Matrix der CABs herum sind die I/O-Puffer angeordnet. Ihre Anzahl hängt vom jeweiligen FPAA ab.

Des weiteren wird die Matrix mit einer Konfigurationslogik und einem Konfigurationsspeicher beschaltet. Häufig wird als Konfigurationsspeicher ein Schieberegister benutzt, das die Konfigurationsdaten dann in die entsprechenden CABs schreibt.

Zur Veranschaulichung wird nachfolgend der schematische Aufbau des AN10E40 dargestellt:

Quelle: Datenblatt des AN10E40, Anadigm Internetseite

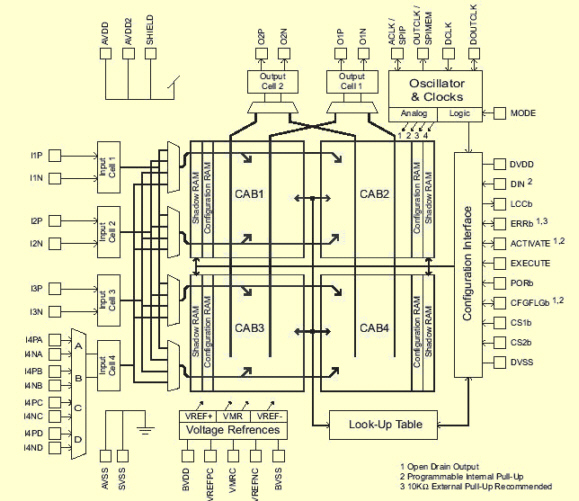

Zur Realisierung des dynamischen Programmierens des AN220E04 wurde ein Shadow SRAM eingeführt, der ebenfalls dem CAB zugeordnet ist. Ist der FPAA in Betrieb und der RAM mit den Konfigurationsdaten beschrieben und er soll rekonfiguriert werden, so nimmt der Shadow-RAM die neuen Konfigurationsdaten an und gibt sie, wenn die Informationen vollständig sind, an den SRAM ab.

Nachfolgend wird zur Veranschaulichung der Aufbau des AN220E04 dargestellt. Das eingezeichnete Konfigurationsinterface und die Look-Up-Table sind Besonderheiten dieses Bausteins und werden in der Produktbeschreibung von Anadigm näher erläutert. (siehe auch Produktbeschreibung AN220E04)

Quelle: Datenblatt der Firma Anadigm