|

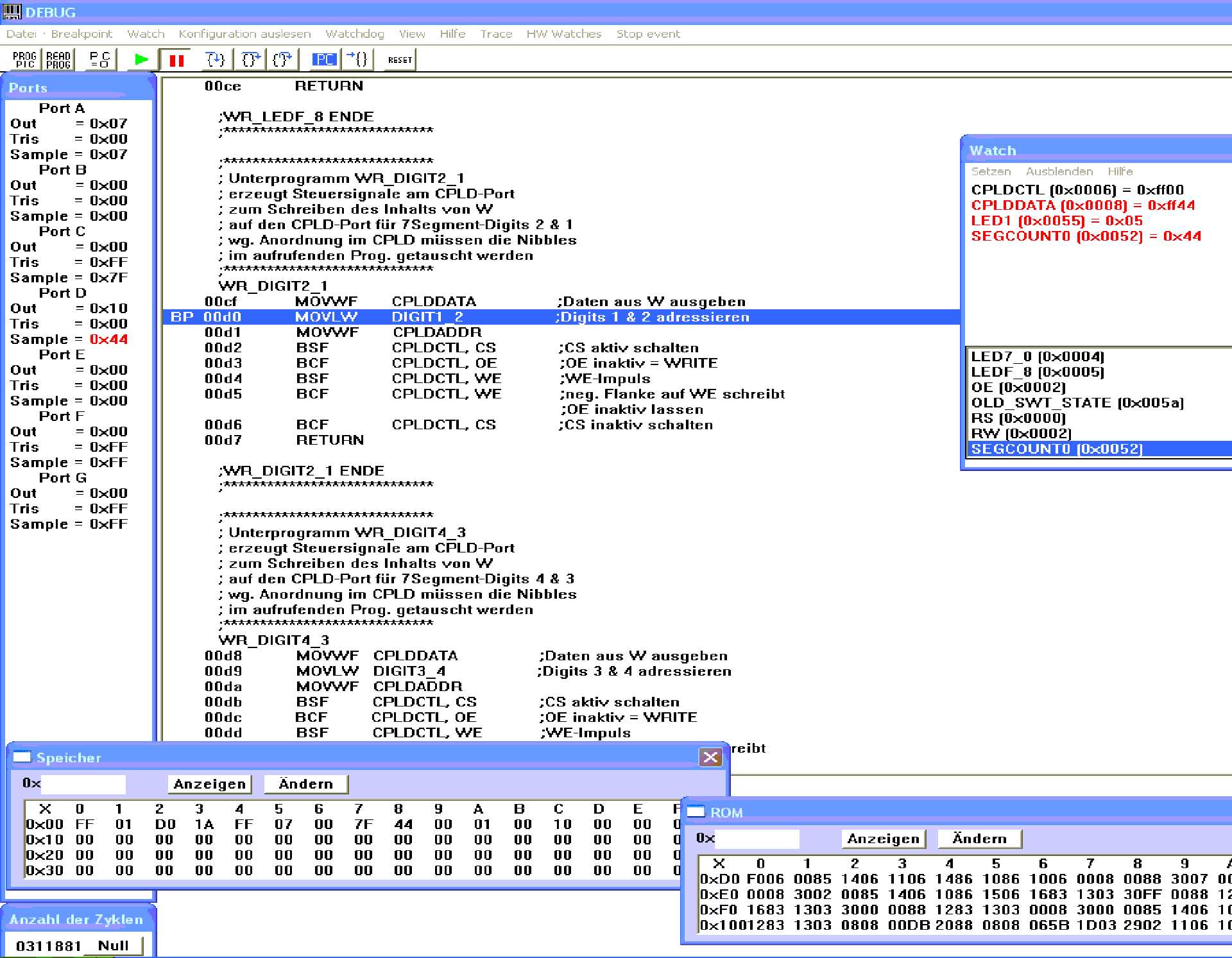

Eine komfortable Debugmöglichkeit für den entwickelten

PIC-kompatiblen, synthetisierbaren Mikrocontrollerkern (s.u.).

-

Das Debugsystem umfaßt ein Hardwareinterface in

VHDL, das im FPGA mit den entsprechenden Komponenten des Controllers

kommuniziert, sowie eine PC-basierte Softwareapplikation, die

dem Benutzer alle relevanten Daten aus dem Controller präsentiert

und ihm die Möglichkeit gibt, auf bequeme Weise alle internen

Funktionen zu kontrollieren.

-

Die Kommunikation zwischen Frontend und Backend

des Debugsystems erfolgt über den JTAG-Port des FPGAs und belegt

keinerlei Ressourcen des Mikrocontrollers.

-

Das Debugsystem, das über einfache Definitionen

im Design aktiviert oder deaktiviert werden kann, erlaubt ein

komfortables Debugging von Software für den FPGA-basierten Mikrocontroller.

--> Paper auf dem IFAC

Workshop 02/2006 ( Brünn)

- Mittlerweile (2007) verfügt das Debugsystem auch über

einen flexibel konfigurierbaren Trace Buffer für Echtzeitaufzeichnungen.

Komfortabel nutzbare Hardware Watches erlauben u.a. die effiziente

Triggerung der Aufzeichnung von Daten im Trace Buffer.

|